有些场景会让工程师极度困惑:原理图、模型、PCB 都没明显问题,仿真一致性很好,第一批样板焊接出来,有的板正常、有的板异常,同一块板重新焊接后又变好,波形时好时坏,完全无法复现仿真。这类差异,通常已经超出 “设计范畴”,进入制造、装配、器件物理工艺的误差区间,也是仿真软件完全无法表达的一类真实变量。

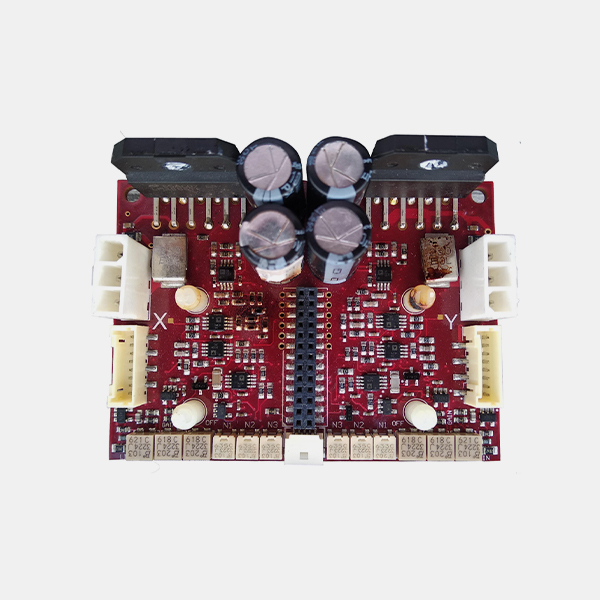

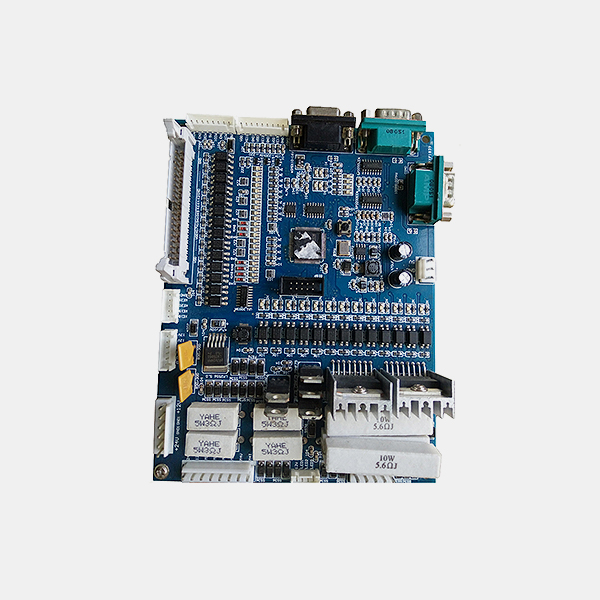

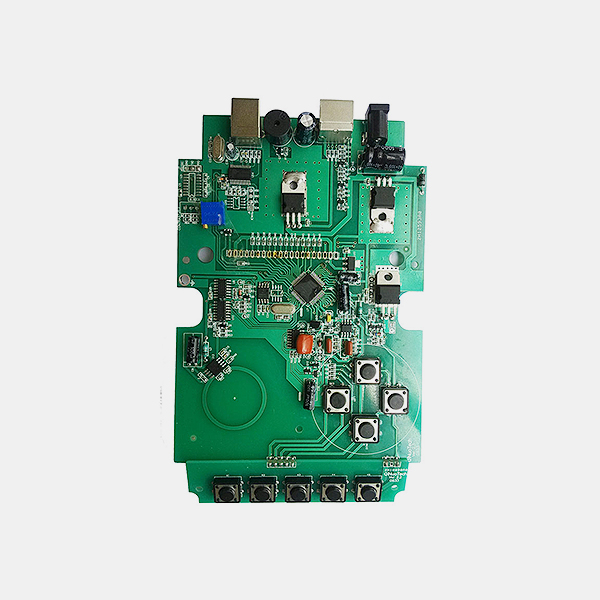

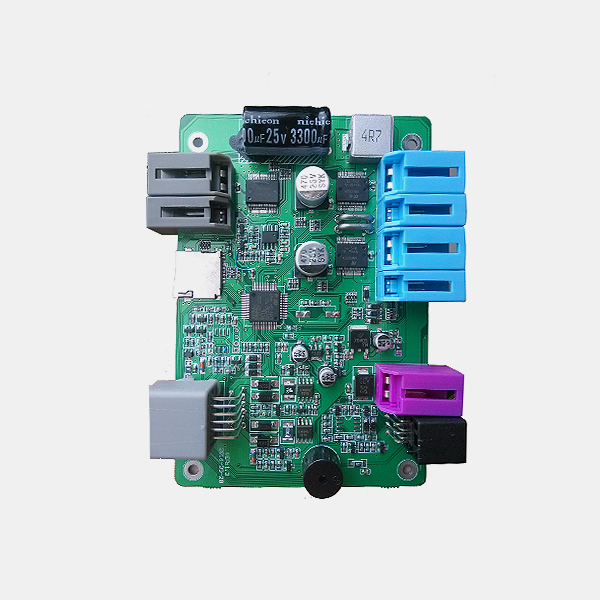

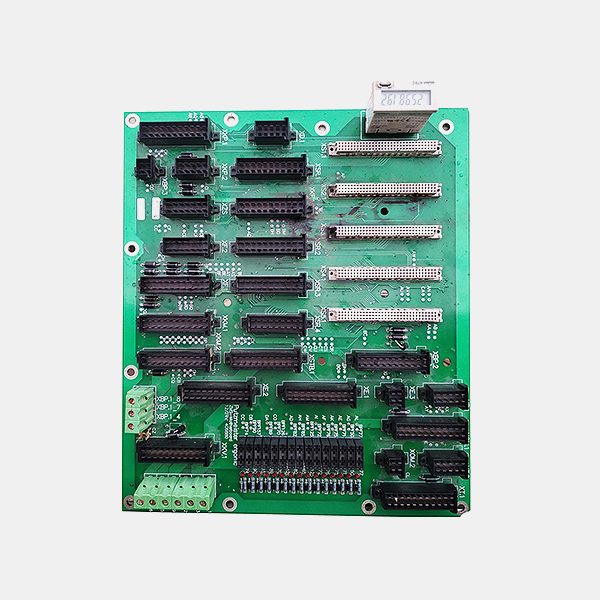

首先是焊接工艺引入的非理想因素。仿真里的器件焊盘与 PCB 连接是 “完美欧姆接触”,无虚焊、无冷焊、无焊锡过多、无焊锡球、无寄生焊锡结构。真实手工焊接或 SMT 工艺中,可能出现:虚焊导致接触电阻忽大忽小,表现为信号时有时无、噪声突增;焊盘锡量过多,在高频引脚、高频管脚上形成额外的焊锡体积,引入额外寄生电容与电感,改变阻抗与谐振点;相邻引脚连锡、焊锡珠,造成隐性短路、漏电流、串扰;插件器件引脚过长,未剪短,引入额外引线电感,对 RF、高频振荡、高速驱动电路影响显著。

尤其是运放、比较器、射频三极管、晶振、MOS 管驱动级,对引脚寄生非常敏感。手工样板常见问题:晶振引脚过长、走线凌乱,导致起振频率偏移、振幅不稳;MOS 管 G 极引脚留太长,振铃加大;小信号回路焊点粗糙、接触电阻偏大,导致零点漂移。这些在仿真中都是 “零变量”,在实物中却是 “随机变量”,自然造成批量差异与仿真偏离。

其次是器件封装与引脚寄生。很多仿真模型只包含芯片裸片的核心参数,不包含封装引线电感、封装电容、引脚电阻。真实芯片的封装(SOT-23、SOP、QFN、BGA、TO-220 等)本身就是一组寄生 RLC 网络。高频、大电流、快速开关场景下,封装寄生会显著改变器件动态特性。例如大功率 MOS 管的封装电感会影响开关尖峰与损耗;高频晶体管封装寄生会改变频率响应;运放封装寄生会影响高频稳定性与噪声。如果模型只提供裸片参数,未包含封装模型,仿真高频特性必然与实测偏离。

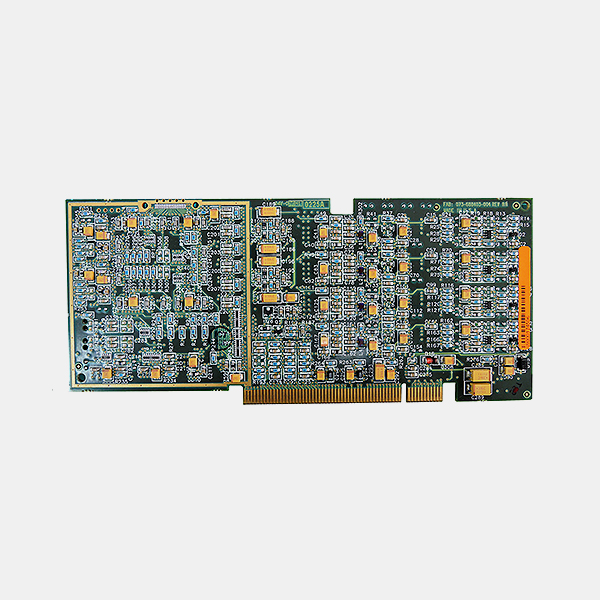

第三类是分立器件的隐性工艺差异。比如同型号、同厂家、不同批次的电容,ESR、ESL 存在波动;电解电容、钽电容的等效参数与频率、电压、老化相关;普通电阻在高频下不再是纯电阻,呈现寄生电感特性;磁珠、电感的阻抗曲线随频率、电流、温度变化。仿真使用的是典型曲线,而实物个体可能偏离典型值,尤其使用非原厂、杂牌、拆机器件时,参数离散性更大,电路工作点、滤波特性、阻尼特性全部偏移。

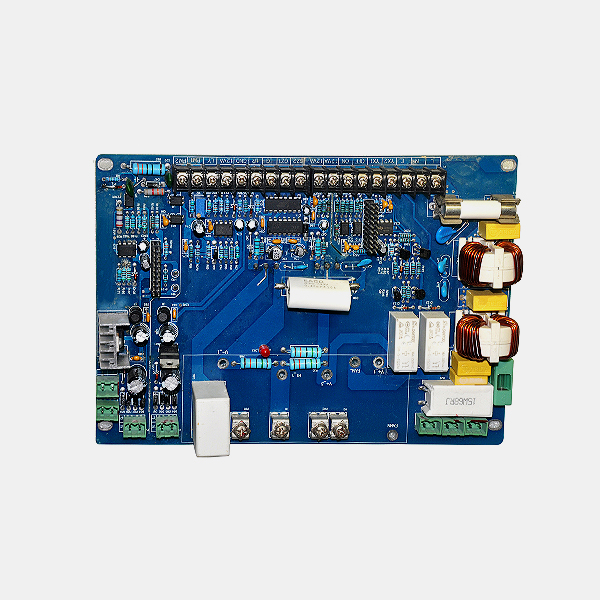

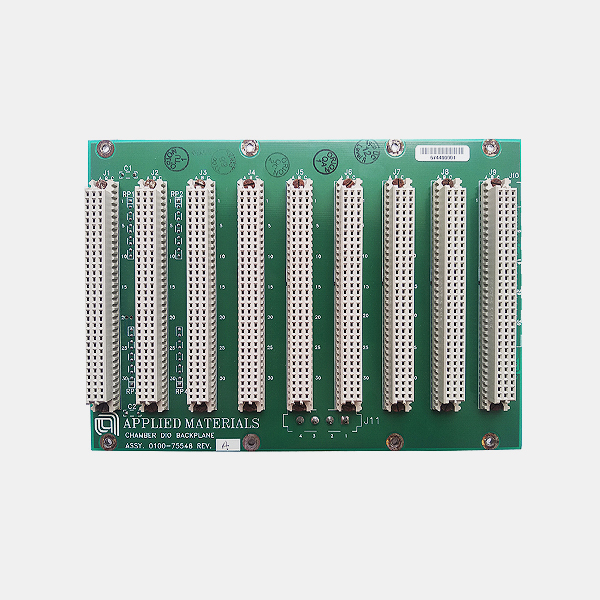

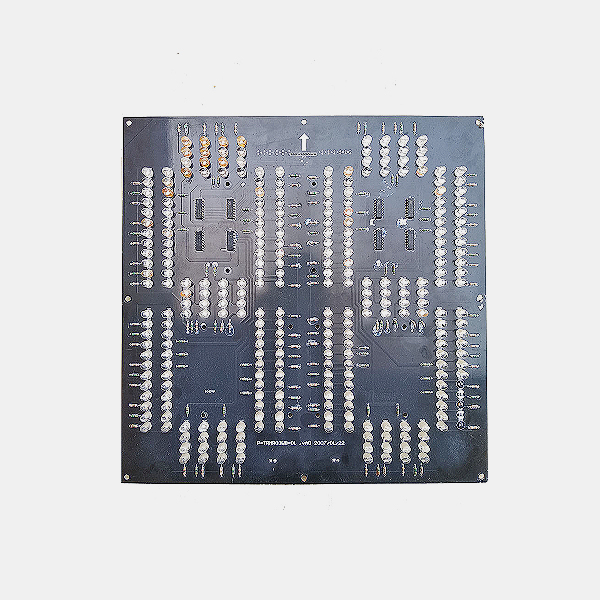

第四类是PCB 板材与制程误差。仿真中默认介电常数 Er 固定、铜厚均匀、线宽精确、阻抗连续。真实 PCB 加工中,线宽公差、铜厚公差、介电常数偏差、阻焊厚度、刻蚀差异,都会改变传输线阻抗、寄生电容、特征阻抗。高频、射频、阻抗控制板(如 50Ω、75Ω、90Ω 差分线),制程误差会直接导致阻抗不连续、反射增大、信号失真,而常规仿真通常使用标称参数,不纳入制程公差分布,因此无法预测阻抗偏移带来的波形差异。

还有机械应力与环境物理影响。PCB 弯曲、形变、器件受力,会改变微裂纹、接触电阻、器件内部应力,进而影响参数;潮湿、灰尘、污染会导致漏电流、表面电阻下降,高输入阻抗电路(如运放、比较器、传感器前端)对漏电流极其敏感。仿真环境是无尘、干燥、无应力的,现实应用中这些因素都会引入额外误差。

针对制造级误差的改善思路,首先是规范工艺与装配:SMT 优先于手工焊,关键板使用回流焊;高频器件引脚剪短,避免长引线;焊点饱满、无虚焊、无连锡;做好清洗与防潮处理。其次是器件选型管控:关键器件固定厂家、固定料号、避免随意替代;高精度电路禁用杂牌分立器件。第三是PCB 制程约束:高频、阻抗板明确阻抗公差、铜厚、板材型号,要求厂家提供阻抗测试报告。第四是样板多板比对:同时焊接 3~5 块样板,排除单块焊接、器件个体差异,判断是设计共性问题还是个案问题。

这篇内容想传递的核心是:仿真只负责 “理想制造水平下的性能”,不负责 “制造误差带来的漂移”。当你排除模型、拓扑、PCB、电源问题后,仍存在差异,一定要往焊接、封装、制程、器件离散性方向排查,这是很多资深工程师最后定位问题的突破口。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)