很多人对 “阻抗控制” 的理解停留在 “线宽多少”,但真正决定阻抗稳定性、成本与良率的,是从原理到叠层、层序、介质、参考平面的一整套逻辑。本文从底层讲透阻抗电路板设计的基础框架,帮你建立系统思维。

一、阻抗是什么?为什么高速板必须控制阻抗?

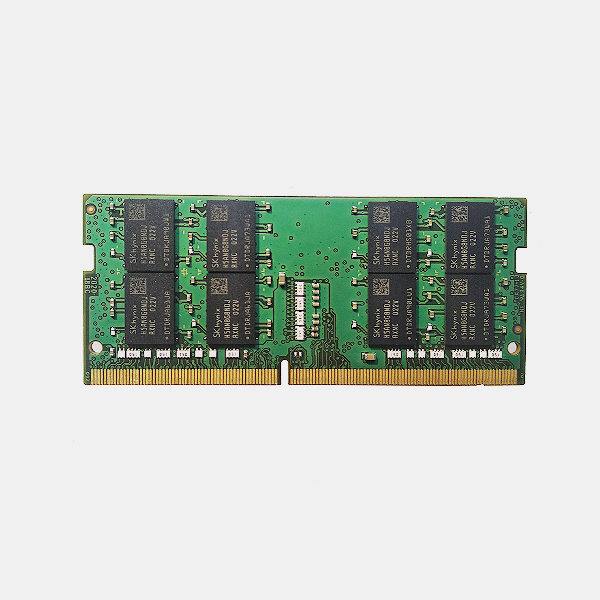

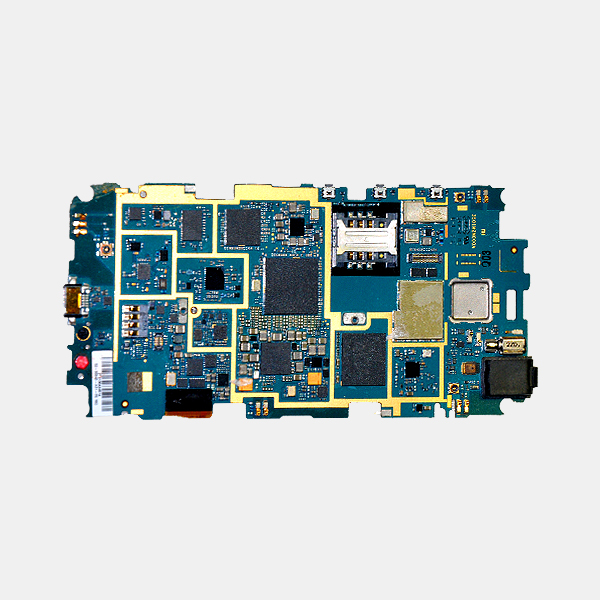

阻抗(Impedance)是信号在传输线上受到的 “总阻力”,由电阻、电感、电容共同决定,单位是欧姆(Ω)。在低频电路中,走线长度远小于信号波长,阻抗影响不明显;但在高速数字电路(如 DDR、PCIe、USB3.0 以上)、射频、微波电路中,信号上升沿极快、频率高,走线本身就成为 “传输线”,阻抗不连续会引发反射、振铃、串扰、时序偏移,直接导致信号完整性(SI)问题,轻则误码,重则系统无法工作。

阻抗控制的本质,就是让传输线的特征阻抗(Z₀)与源端、负载端阻抗匹配,通常常见标准有 50Ω(射频)、75Ω(视频)、90Ω/100Ω(差分对)等。控制不准,再好的芯片、再快的速率也跑不起来。

二、特征阻抗的核心影响因素:线宽、介质厚度、介电常数、铜厚

特征阻抗不是拍脑袋定的,而是由物理结构与材料共同决定,核心公式可简化理解为:Z₀ ∝ √(L/C)其中 L 是单位长度电感,C 是单位长度电容。影响 L 和 C 的关键参数有四个:

走线宽度(W)线越宽,与参考平面的耦合越强,电容 C 越大,阻抗 Z₀越低;线越窄,阻抗越高。这是工程师最直观的调节手段,但不能无限调窄 —— 线太细会影响载流能力、蚀刻公差、阻抗一致性,还会提升成本。

介质厚度(H)走线与参考平面之间的介质层越厚,耦合越弱,电容 C 越小,阻抗 Z₀越高;介质越薄,阻抗越低。介质厚度对阻抗的敏感度非常高,是叠层设计中影响最大的变量之一。

介电常数(Dk/εr)材料 Dk 越大,电场集中在介质中越多,电容 C 越大,阻抗 Z₀越低。常见 FR-4 的 Dk 约 4.2–4.5,高速材料如罗杰斯、松下 Megtron 系列 Dk 更低(3.0–3.8),阻抗更稳定,但成本更高。

铜厚(T)铜厚影响走线的 “有效宽度” 与边缘场分布,铜越厚,等效线宽略增,阻抗略降;铜薄则阻抗略升。常规 1oz(35μm)、2oz(70μm)铜厚对阻抗影响有限,但在细线、薄介质设计中不可忽略。

这四个参数相互牵制,改一个就要联动调其他,这就是阻抗设计的 “平衡艺术”。

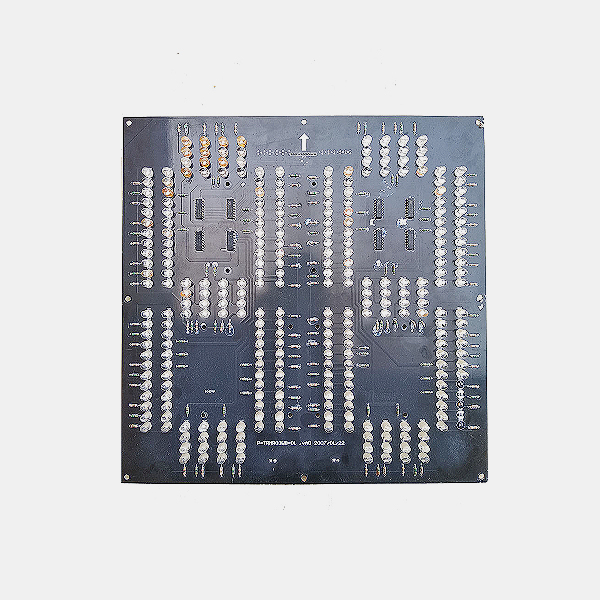

三、阻抗电路板的关键:叠层设计(Stackup)

叠层是阻抗控制的 “骨架”,很多项目后期阻抗超标、成本失控,根源就是前期叠层没定好。作为 PCB 工程师,叠层设计要同时满足:阻抗目标、层序对称、散热、载流、成本、加工性。

1. 参考平面必须完整、连续

阻抗走线必须有明确的参考平面(GND 或 Power),参考平面不连续(开槽、挖空、过孔密集区)会导致阻抗突变、回流路径变长,引发严重 SI 问题。差分对尤其忌讳跨分割。

2. 层序对称,减少翘曲与阻抗漂移

多层板(4 层及以上)应尽量对称叠层,比如:

4 层板:Top - GND - Power - Bottom

6 层板:Top - GND - Sig - Sig - GND - Bottom对称结构可降低压合翘曲,保证介质厚度均匀,从而提升阻抗一致性。

3. 介质厚度选择要兼顾阻抗与成本

例如要做 90Ω 差分线,若用常规 FR-4、1oz 铜,工程师需要根据目标阻抗反推线宽与介质厚度。介质越薄,线宽可以越宽,加工公差更容易控制,良率更高,但层数可能增加;介质厚,线宽变细,成本低但公差敏感。

很多低成本方案就是通过 “合理叠层 + 标准材料” 实现阻抗达标,而不是盲目上高速料。

四、单端阻抗 vs 差分阻抗:设计要点差异

实际项目中,阻抗分两大类,设计逻辑不同:

1. 单端阻抗(Single-ended Z₀)

常见 50Ω,用于时钟、控制信号、部分射频线。设计要点:

保证单侧参考平面完整;

线宽均匀,避免突然变宽 / 变窄;

远离其他走线,减少串扰;

过孔、焊盘、测试点都会造成阻抗不连续,需做补偿(如反焊盘、短桩控制)。

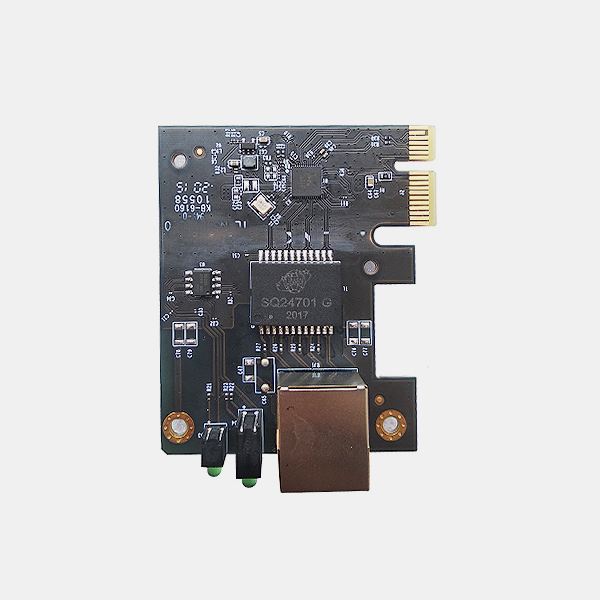

2. 差分阻抗(Differential Zdiff)

常见 90Ω、100Ω,用于高速差分信号(USB、HDMI、M-LVDS、以太网等)。差分阻抗与线宽、线距、介质厚度、Dk 都相关,公式可简化理解为:Zdiff ≈ 2 × Z₀(单端)× √(1 - K)其中 K 是耦合系数,线距越小,耦合越强,K 越大,差分阻抗越低。

设计要点:

差分对要等长、等距、平行,长度误差通常控制在 5mil 内(高速更严);

线距决定耦合度,不能随意改;

避免跨分割,避免单侧靠近干扰源;

过孔数量尽量一致,过孔 stub 要控制(如背钻)。

五、阻抗公差:为什么 ±10% 不是随便定的?

客户常要求阻抗公差 ±10%、±8%、±5%,公差越严,成本越高、良率越低。作为工程师,要懂得 “合理设公差”,而不是一味追求极致。

±10%:常规 FR-4、常规工艺可实现,成本低、良率高,适合多数消费电子、工业控制。

±8%:对叠层、线宽、介质厚度控制更严,需要更稳定的压合与蚀刻,成本略升。

±5%:属于高精度阻抗,通常需要高速材料、激光直接成像(LDI)、严格过程控制,多用于通信、服务器、高端射频,成本明显上升。

阻抗公差的本质是 “加工能力边界”,工程师要根据信号速率、系统预算、量产规模来定,而不是盲目抄高端板的标准。

阻抗电路板设计不是 “调线宽” 那么简单,它是叠层、材料、公差、工艺、信号完整性的综合工程。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)