在电子设备研发中,PCB 设计堪称 “隐形地基”—— 一个看似不起眼的布线失误,可能导致产品过不了安规认证、抗干扰能力差,甚至直接引发发热烧毁。今天就从安规距离、抗干扰技巧、布局布线原则到热设计和工艺细节,用最易懂的语言拆解 PCB 设计的核心要点,新手也能快速上手!

一、安规距离:

守住电气安全的第一道防线

安规距离是 PCB 设计的 “红线”,直接关系到设备是否会发生短路、放电等安全隐患,主要包括电气间隙和爬电距离两大核心指标。

关键参数速查

爬电距离

:输入电压 50V-250V 时,保险丝前 L-N≥2.5mm;250V-500V 时≥5.0mm。

电气间隙

:输入电压 50V-250V 时,保险丝前 L-N≥1.7mm;250V-500V 时≥3.0mm。

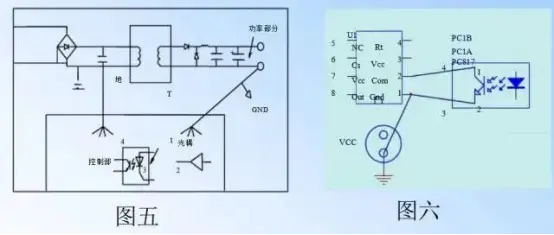

特殊要求:一次侧对二次侧≥6.4mm(光耦、Y 电容等间距不足需开槽);变压器两级间≥6.4mm,加强绝缘需≥8mm。

不同电压对应的最小爬电距离可参考下图,精准匹配需求更省心:

电压范围与推荐最小爬电距离

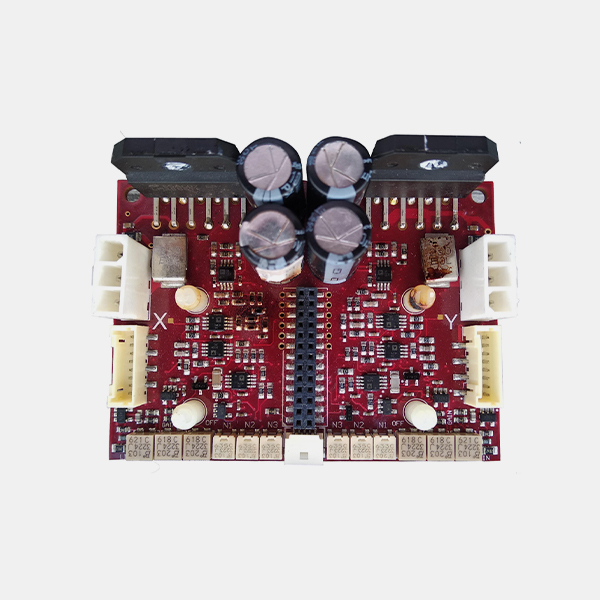

二、EMC 抗干扰:

拒绝 “电磁骚扰”,让信号更稳定

电子设备的 “电磁兼容性” 直接影响使用体验,做好抗干扰设计,才能避免信号紊乱、测试失败。

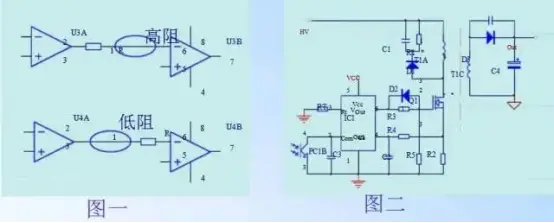

核心技巧 get 起来

短线优先,就近布局

驱动电阻靠近 MOS 管,电流取样电阻靠近 IC 引脚,运算放大器周边元件缩短高阻抗线路,减少干扰接收面积。

长线路抗干扰布局

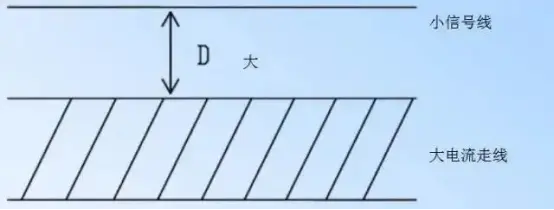

强弱分离,保持距离

小信号走线与大电流走线间距≥2.0mm,忌平行布线,避免相互干扰。

小信号线与大电流走线间距

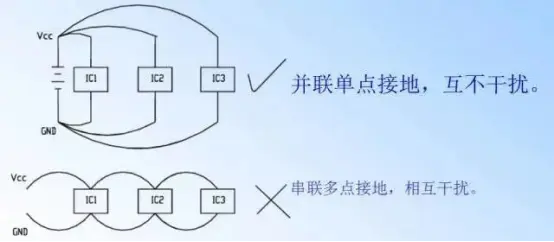

接地有讲究

多个 IC 供电采用并联单点接地,避免串联接地的相互干扰;控制回路与功率回路分开接地,散热器优先单点接地,提升噪声抑制能力。

接地方式对比图

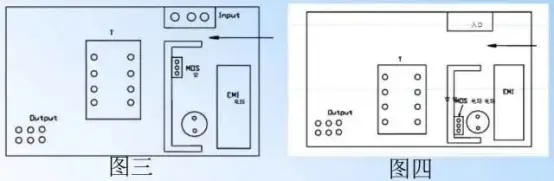

远离干扰源

光电耦合器件远离大电流走线、变压器等强电场、强磁场器件;MOS 管、变压器尽量远离输入端子,避免电磁辐射直接作用于输入端导致 EMI 测试失败。

MOS 管、变压器布局对 EMI 的影响图

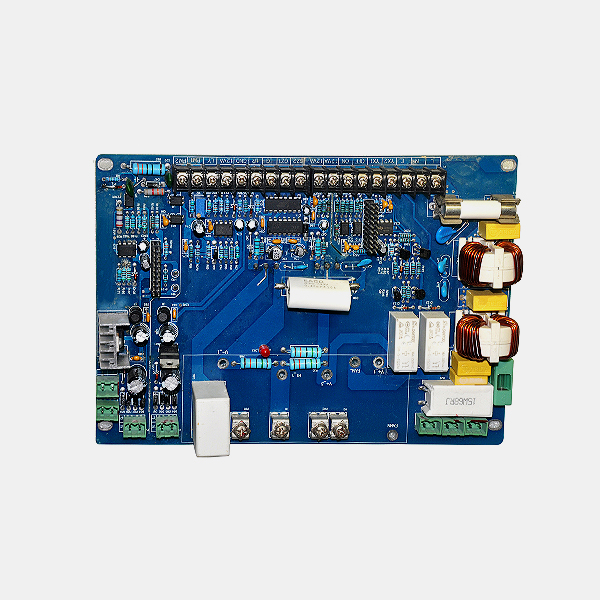

三、布局布线:

细节决定成败,这些原则要记牢

合理的布局布线不仅能提升抗干扰能力,还能简化装配工艺、延长产品寿命。

整体布局要点

散热片分布均匀,保证风路通畅;电容、IC 等远离散热器、功率电阻等热元件。

输入 / 输出线长短一致,预留插头线扣空间;电路板边缘的元器件距板边≥2mm。

可调元件(电位器、微动开关等)需匹配整机结构,机外调节元件要与机箱面板旋钮位置对应。

布线黄金法则

线宽匹配电流:50μm 厚铜箔 1mm 宽可通 1A 电流,70μm 厚可通 1.5A,电源线尽量加粗缩短。

拐角要圆滑:避免直角、锐角走线,高频电路中弧形拐角更利于电气性能。

特殊区域禁布线:电感、电流环、金属膜电阻下方不宜走高压线;信号线不穿过变压器、散热片。

过孔处理:大电流区域多增加过孔并加锡,提升载流能力;单面板跳线与低压元件保持安规距离,距散热片≥1mm。

控制回路与功率回路单点接地

四、热设计与工艺:

兼顾稳定性与可制造性

热设计关键

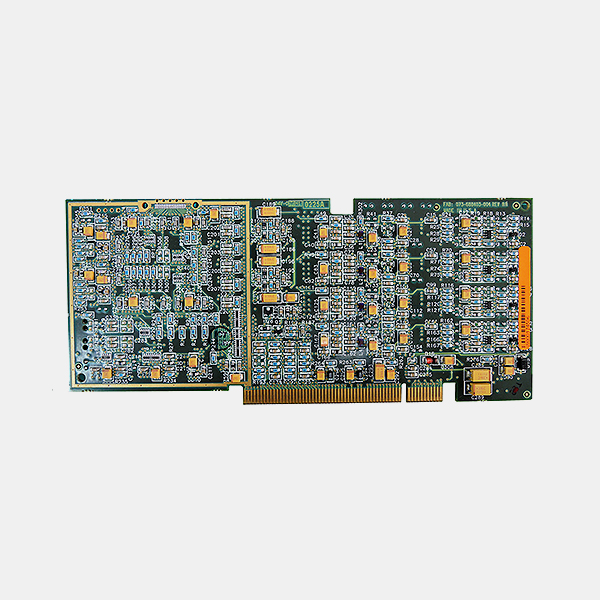

工艺细节不能漏

过锡炉方向需用箭头标注,DIP 封装 IC 摆放方向与过锡炉方向垂直,SOP 封装相反。

贴片元件需设置校正标记(每块板至少 2 个,位于对角),提升贴装准确性。

焊盘尺寸合理:外径一般不少于(引线孔径 + 1.2)mm,高密度数字电路可最小取(d+1.0)mm;孔径大于 2.5mm 的焊盘适当加大,避免虚焊。

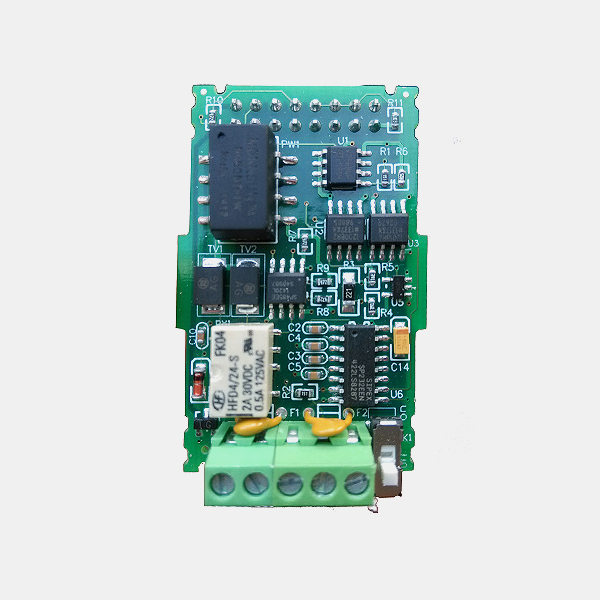

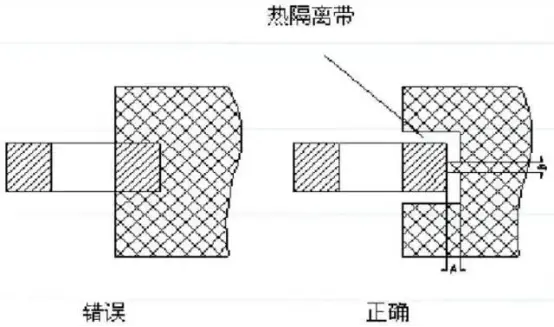

SMD 器件引脚与大面积铜箔连接时,需做热隔离处理,防止焊接时因热量集中损坏元件。

SMD 器件热隔离处理

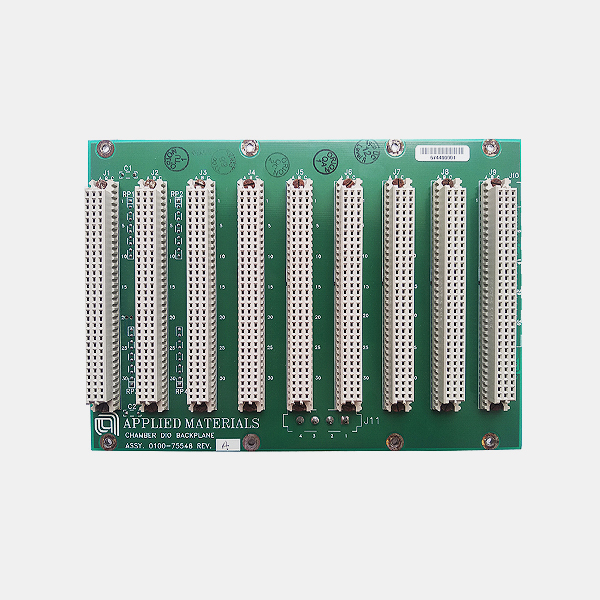

五、常见问题案例:

避开这些 “坑”,设计更高效

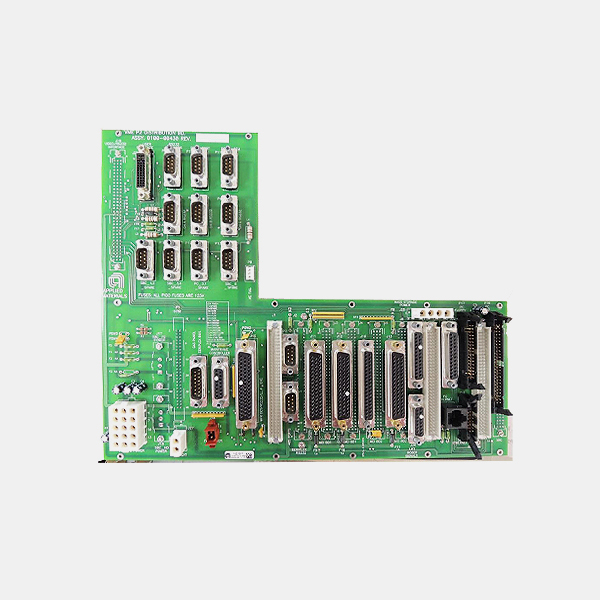

布局失误

六层板将 PWM IC 与光耦放在 MOS 管下方,仅隔 2.0mm PCB 导致严重干扰,改进后移开干扰源,问题解决。(此处插入文档中图 26、27:布局改进前后对比图)

走线不当

电流环包围面积过大,接收干扰过多;PWM IC 的采样线与驱动线平行走线,导致相互干扰,缩短走线、避免平行后恢复正常。

PCB 设计是一门 “细节活”,掌握安规、EMC、布局布线的核心要点,就能有效降低设计风险、提升产品可靠性。收藏这份指南,

下次设计时直接对照参考,效率翻倍!

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)