随着 5G、人工智能、高速数据传输等技术的普及,PCB 工作频率不断提升,部分场景已进入毫米波频段,损耗控制成为 PCB 设计与制造的核心难题。PCB 损耗不仅会导致信号衰减、眼图塌陷、时序错误,还会引发局部过热,降低设备可靠性与使用寿命。因此,需从材料选型、设计优化、工艺管控、仿真验证四大维度,采取系统性策略,精准控制 PCB 损耗,兼顾性能与成本。

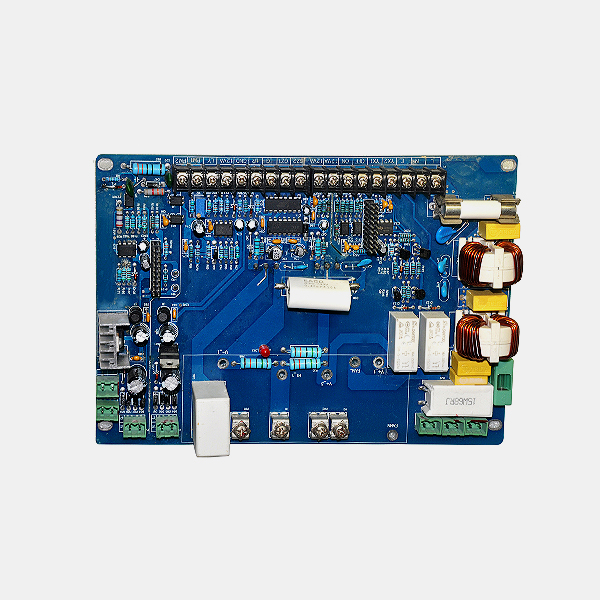

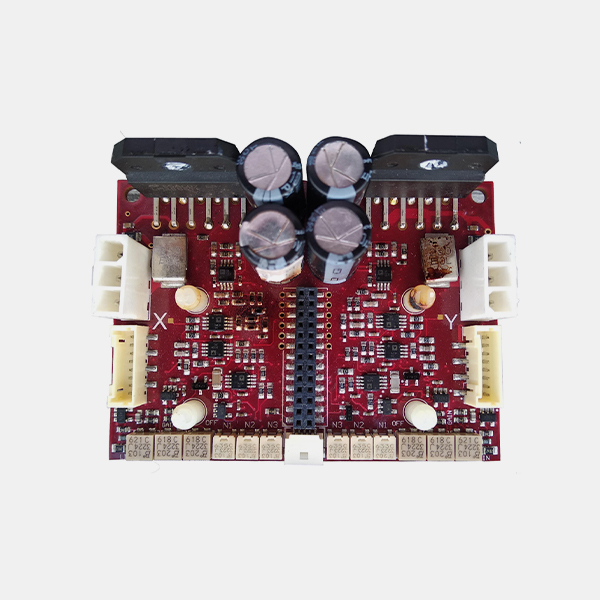

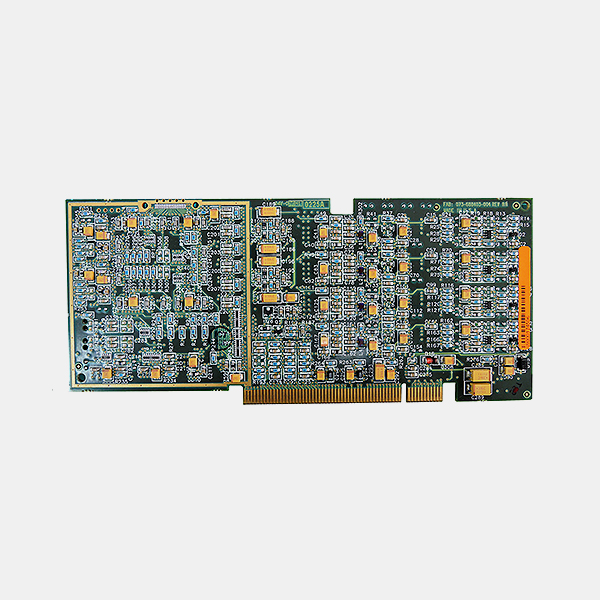

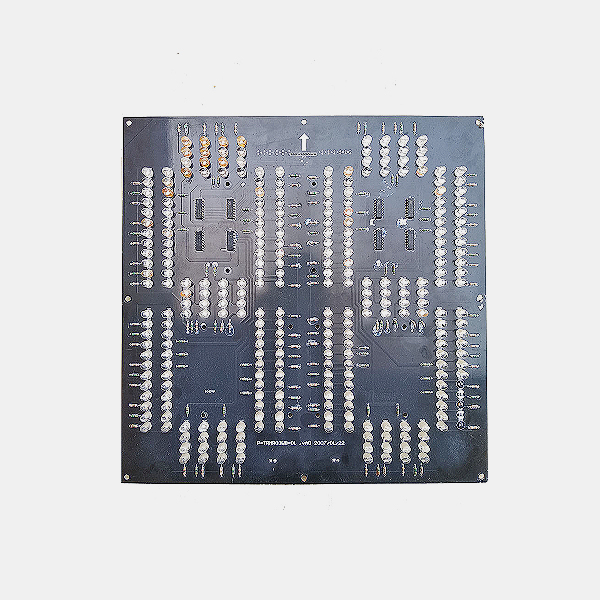

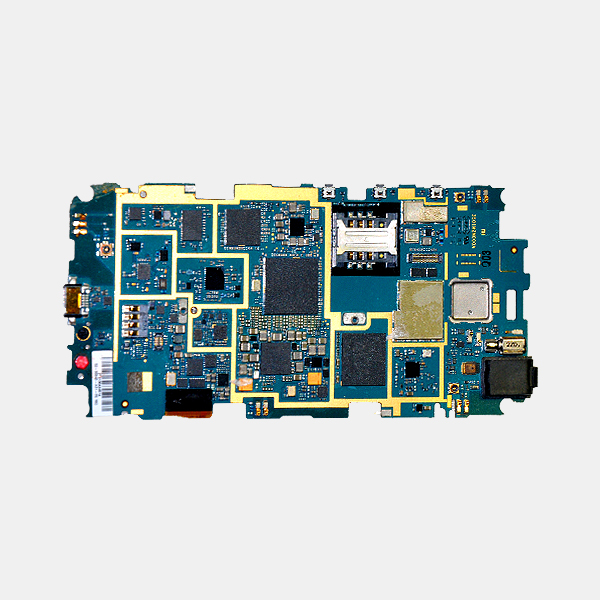

材料选型是降低 PCB 损耗的基础,核心在于优选低损耗基材与铜箔,从源头减少能量损失。基材方面,需根据工作频率匹配对应材料:低频场景(<1GHz)可选用常规 FR-4 板材,平衡成本与性能;高频场景(1-10GHz)推荐使用改性环氧、PPO 等中低损耗板材(Df≤0.01);毫米波频段(>10GHz)必须选用 PTFE、LCP、陶瓷填充等高频低损耗板材(Df≤0.002),可使介质损耗降低 80% 以上。铜箔方面,高频场景优先选用超低轮廓(VLP/ULP)铜箔,将表面粗糙度 Ra 控制在 1μm 以内,减少趋肤效应带来的导体损耗;避免使用标准压延铜箔,其粗糙表面会使高频损耗增加 20%-30%。

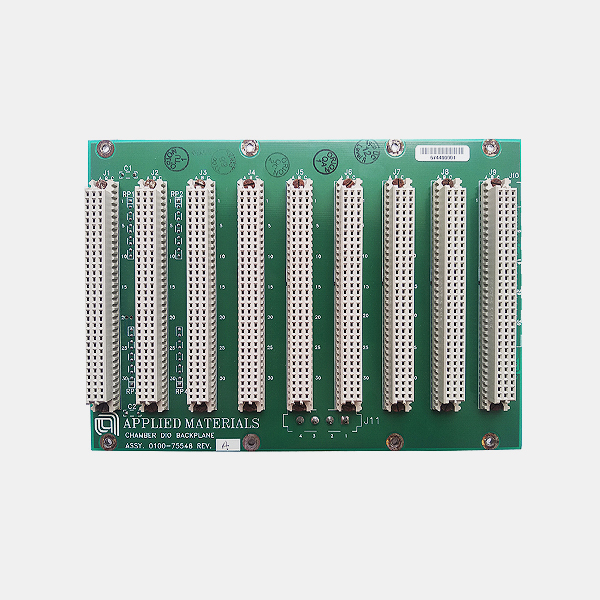

设计优化是损耗控制的核心环节,通过合理的布局、布线与叠层设计,减少损耗诱因,抑制能量衰减。布局上,遵循 “短、直、近” 原则:缩短高速信号线长度(损耗与长度成正比),避免冗余走线;高速路径远离电源噪声、接地干扰源;功率器件、高频元件就近布局,减小信号环路面积,降低辐射与耦合损耗。布线时,控制线宽与铜厚:在阻抗匹配前提下,适当增加线宽(扩大导电面积)、选用 1oz 或 2oz 厚铜箔,降低导体直流电阻;严格控制走线间距,遵循 “3W 原则”(线间距≥3 倍线宽),减少邻近效应与串扰损耗。叠层设计上,优先采用带状线结构(信号线嵌入两层参考平面之间),替代微带线结构,可降低辐射损耗 12dB 以上;关键高速层靠近接地平面,减小介质厚度,降低介质损耗;合理设计电源 / 地平面,保证回流路径完整,减少寄生电感与阻抗失配。此外,减少过孔数量,必须使用时优化过孔设计(如背钻去除残桩、减小过孔尺寸),避免过孔引入的阻抗不连续与额外损耗。

工艺管控是损耗控制的关键保障,精细化制造工艺可避免因加工误差导致的损耗超标。蚀刻工艺上,采用垂直连续蚀刻线,保证喷淋压力、药水浓度均匀,严格控制蚀刻因子,使走线截面接近矩形,避免侧壁粗糙、锯齿或梯形结构,减少导体损耗。表面处理方面,高频 PCB 严禁使用喷锡工艺(表面粗糙、厚度不均),优先选用沉金、沉银等工艺,保证表面平整、厚度均匀,降低接触损耗与高频衰减。层压工艺上,优化层压压力与温度,保证低粗糙度铜箔与介质的结合力,避免铜箔脱落或表面氧化;严格控制介质厚度均匀性,误差控制在 ±5% 以内,防止因厚度波动导致的损耗差异。

仿真验证是损耗控制的重要手段,在设计阶段提前预测损耗,优化方案,避免后期返工。利用电磁场仿真工具(如 ADS、HFSS、SIwave),基于实际叠层方案、材料 Dk/Df 曲线(而非标称值)、铜箔粗糙度模型,精确建模信号传输路径,预估导体损耗、介质损耗、辐射损耗占比。通过仿真优化线宽、线间距、过孔参数、叠层结构,迭代出低损耗设计方案;同时预留测试结构(如耦合器、阻抗测试线),量产前通过矢量网络分析仪实测 S 参数(插入损耗、回波损耗),验证仿真结果,建立闭环优化机制。

PCB 损耗控制是一项贯穿材料、设计、工艺、仿真全流程的系统性工作。材料选型需精准匹配频率需求,优选低损耗基材与光滑铜箔;设计优化需从布局、布线、叠层入手,减少损耗诱因;工艺管控需精细化,严控蚀刻、表面处理、层压等关键工序;仿真验证需提前介入,实现设计与实测的闭环优化。在实际应用中,需结合设备性能需求、成本预算与量产能力,制定差异化损耗控制方案,平衡损耗、性能与成本,助力高频高速电子设备稳定可靠运行。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)