在高速 / 高频 PCB 设计中,阻抗控制是叠加设计的核心目标,而层压介质选型与厚度设计是实现精准阻抗控制的关键。很多工程师在叠加设计时,忽视介质特性与阻抗的关联,导致层压后阻抗偏差超标(>±5%),引发信号反射、串扰、传输误码等问题。本文从阻抗控制原理、介质选型、层压叠加参数设计三方面,解析多层 PCB 层压叠加的阻抗控制技巧。

一、层压叠加中阻抗控制的基本原理

高速信号在 PCB 上以 ** 微带线(表层)或带状线(内层)传输,其特性阻抗由介质介电常数(Dk)、介质厚度(H)、线宽(W)、铜箔厚度(T)** 共同决定,核心公式如下:

微带线(表层):Z0=(87/√(Dk+1.41))×ln (5.98H/(0.8W+T))

带状线(内层):Z0=(60/√Dk)×ln (4H/(0.67π(W+T))))

阻抗控制目标是将特性阻抗稳定在目标值 ±5%(普通高速)或 **±3%**(高频射频),常用目标值:单端 50Ω、差分 100Ω。从公式可知,介质 Dk 与 H 是影响阻抗的核心变量,层压叠加设计需优先把控这两个参数。

二、层压介质的选型标准与特性对比

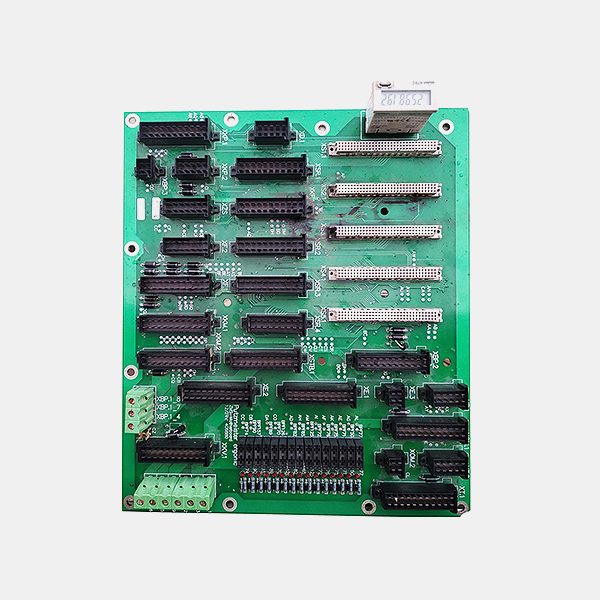

层压介质包括芯板(Core)与半固化片(PP),二者材质需匹配,确保层压后 Dk 均匀、稳定。

普通场景(<5GHz)介质选型

芯板 / PP 材质:普通 FR-4,Dk=4.4±0.2(1GHz),Df=0.02,成本低、加工性好;

厚度选择:表层微带线 H=0.2~0.3mm,内层带状线 H=0.15~0.2mm,平衡阻抗精度与工艺可行性;

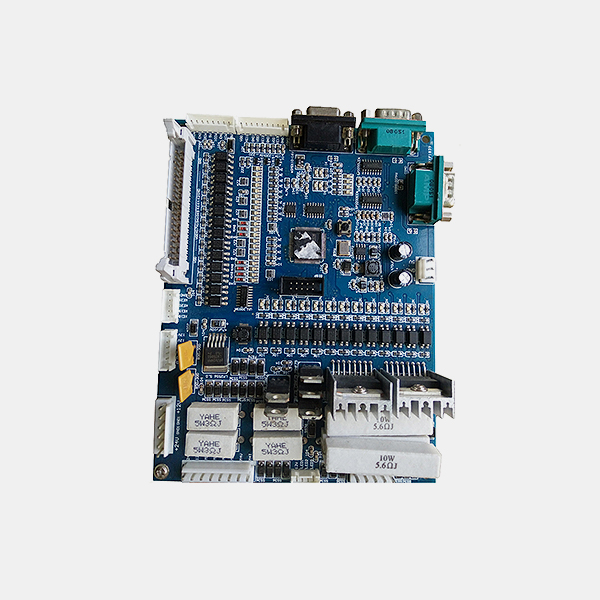

适用场景:1Gbps~5Gbps 高速数字电路、普通工业控制板。

高频场景(≥5GHz)介质选型

芯板 / PP 材质:高频专用基材(罗杰斯 4350B、Isola 370HR、PTFE),Dk=2.2~3.5(10GHz),Df=0.001~0.004,高频下损耗低、Dk 稳定;

厚度选择:表层 H=0.127~0.254mm(精准公差 ±0.01mm),内层 H=0.1~0.15mm,严格控制阻抗波动;

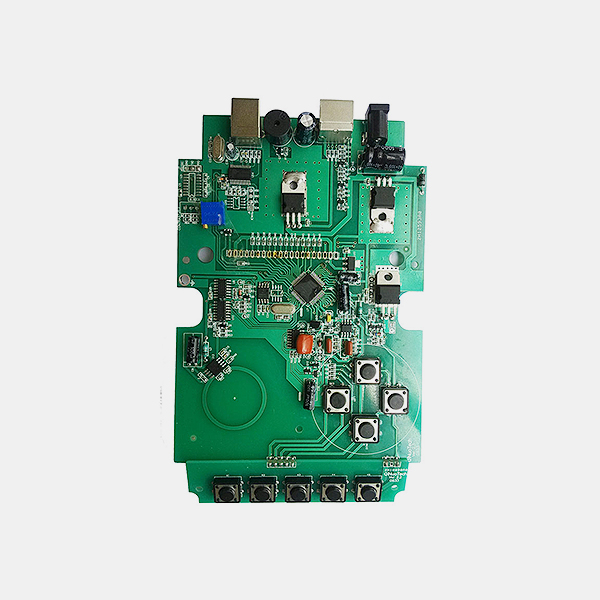

适用场景:5G 射频模块、WiFi 7、10Gbps 以上高速通信板。

介质选型避坑要点

芯板与 PP 材质必须一致:避免 FR-4 芯板 + 高频 PP,层压后 Dk 不均,阻抗偏差超标;

严控 Dk 公差:普通 FR-4 Dk 公差≤±0.2,高频基材≤±0.1,确保阻抗一致性;

温度系数优先:选择 Dk 温度系数≤±50ppm/℃的介质,宽温环境(-40℃~+85℃)下阻抗稳定。

三、层压叠加的阻抗匹配参数设计(实操技巧)

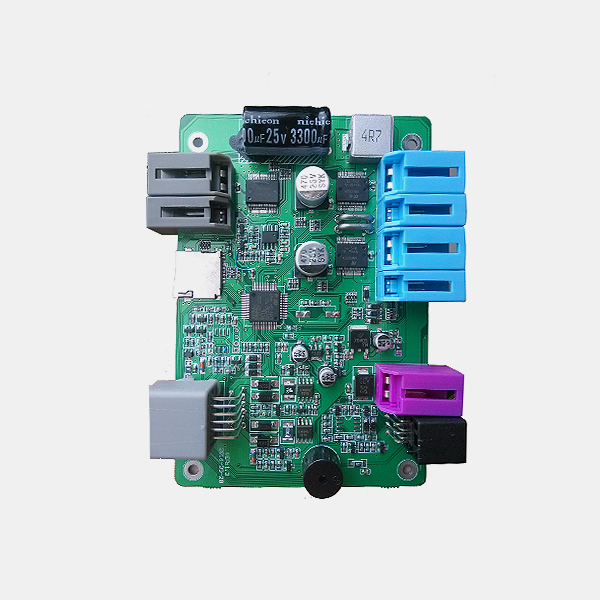

以 **6 层高速板(单端 50Ω、差分 100Ω、FR-4 基材)** 为例,详解层压叠加参数设计:

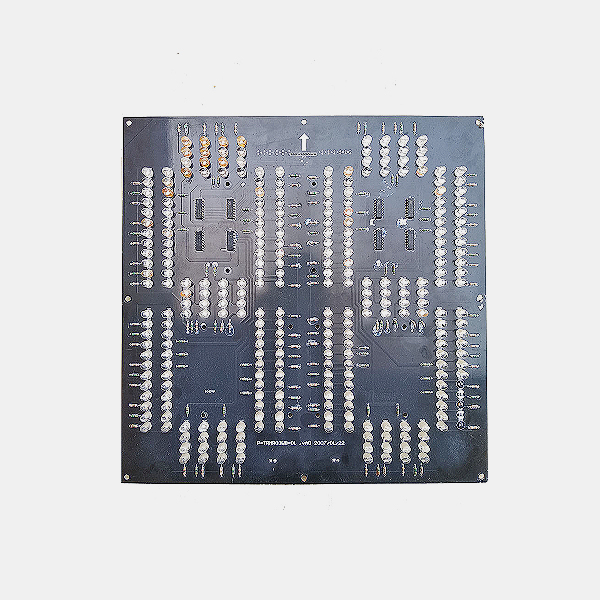

层序规划(对称结构):Top (信号,微带线) → PP (H1=0.2mm) → GND (1oz) → PP (H2=0.15mm) → PWR (1oz) → PP (H2=0.15mm) → GND (1oz) → PP (H1=0.2mm) → Bottom (信号,微带线)。

线宽计算(50Ω 单端,FR-4 Dk=4.4,铜厚 1oz)

表层微带线(H=0.2mm):代入公式,计算得线宽 W=0.22mm(公差 ±0.01mm);

内层带状线(H=0.15mm,上下介质):线宽 W=0.18mm(公差 ±0.01mm)。

阻抗补偿设计

层压预补偿:考虑层压后介质压缩(压缩率 5%~8%),设计时 H 增加 5%,如目标 0.2mm,设计 0.21mm;

线宽预补偿:蚀刻侧蚀量 0.02mm,设计线宽增加 0.02mm,保证成品线宽达标。

验证与优化

仿真验证:用 ADS、HFSS 扫描介质厚度、Dk 公差,确认阻抗波动≤±4%;

试产校准:小批量试产,TDR 测试阻抗,微调介质厚度与线宽,固化参数。

四、层压叠加阻抗控制的常见误区

忽视介质压缩率:层压后介质压缩 5%~8%,直接采用目标厚度,导致阻抗偏高;

芯板与 PP 材质不匹配:Dk 不均,阻抗波动超 ±10%,高速信号眼图闭合;

公差设计过松:介质厚度公差 ±0.05mm,线宽公差 ±0.02mm,阻抗偏差超标;

内层信号远离地层:带状线上下介质厚度不均,阻抗不稳定,串扰加剧。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)