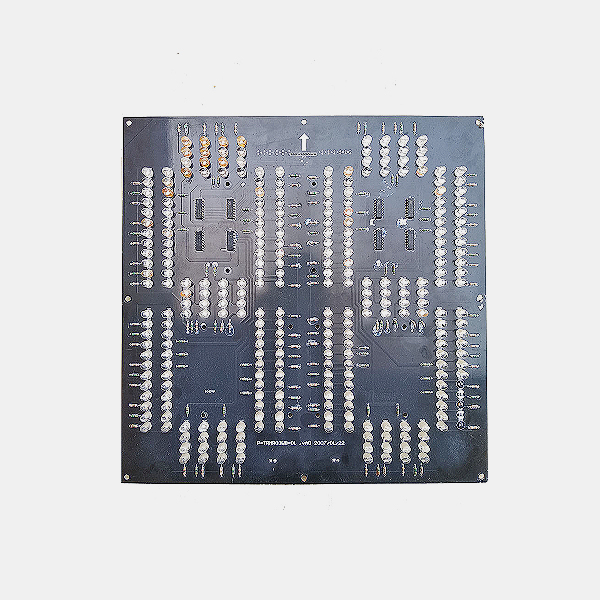

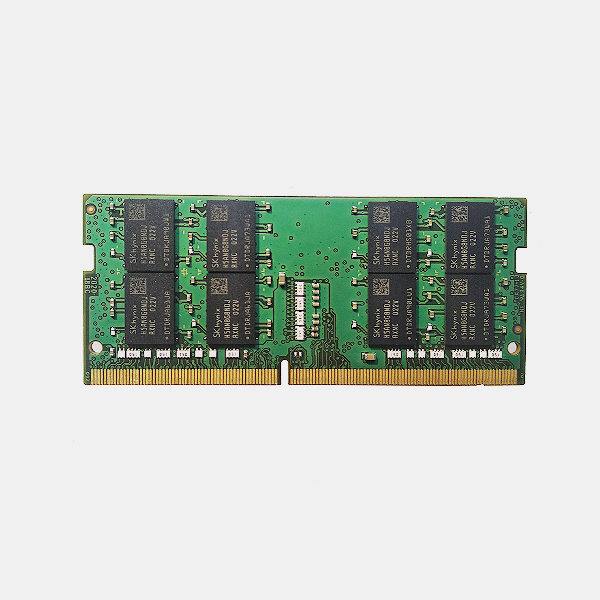

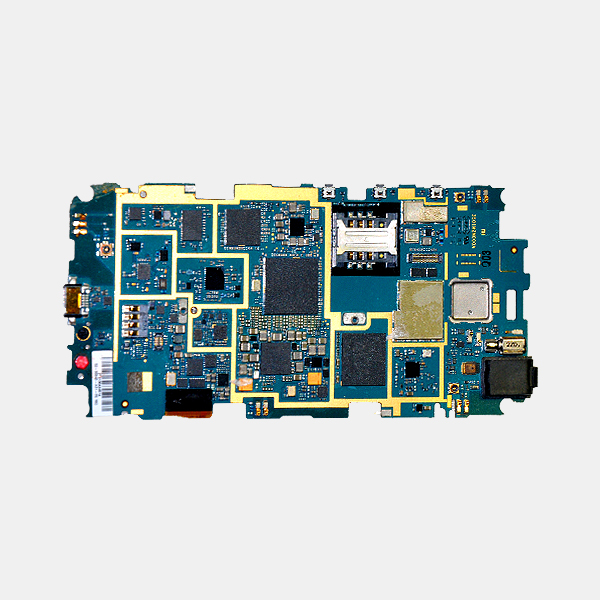

在多层PCB的实际研发和生产中,即便前期做了完善的设计仿真,也难免出现电力完整性故障,比如设备开机死机、芯片发热严重、信号干扰大、电压波动超标等。很多工程师面对这类故障时,往往无从下手,要么盲目更换电容,要么随意修改走线,不仅无法解决问题,还会延长研发周期。

首先梳理多层PCB电力完整性最常见的四类故障,也是行业内故障率最高的问题:第一类是IR压降超标,表现为芯片供电电压低于标称值,芯片工作异常、发热,大负载工况下直接宕机;第二类是电源噪声与纹波超标,表现为信号波形失真、设备抗干扰能力差,敏感模拟电路出现数据漂移;第三类是地弹噪声与同步开关噪声,表现为高速芯片工作时出现逻辑错误、数据丢包,高频段信号误码率高;第四类是电磁干扰(EMI)超标,电源噪声通过辐射或传导干扰周边设备,无法通过电磁兼容测试。

针对IR压降超标故障,诊断和优化的核心是定位高阻抗供电路径。首先用万用表测量芯片电源引脚和电源模块输出端的电压差,确定压降数值,判断是否超出芯片容差范围;然后通过PCB设计文件,排查供电路径的铜箔宽度、铜箔厚度、过孔数量,常见诱因是电源层铜箔过窄、大电流路径过孔数量不足、局部平面被切割导致阻抗升高。优化方案很直接:加宽电源铜箔、增加并联过孔、更换更厚的铜箔(比如从1oz换成2oz)、修复被切割的电源平面,保证大电流路径的低阻抗。对于大功率器件,可在供电路径上额外铺铜,进一步降低电阻,减少压降损耗。

电源噪声与纹波超标故障,是最容易出现但也最容易误判的问题,诊断需要借助专业工具,示波器是核心测试设备,测试时要采用差分探头,靠近芯片电源引脚测量,避免长线测试引入外界干扰,精准读取噪声幅值和纹波频率。常见诱因分为三种:一是去耦电容布局过远、容值搭配不合理,高频噪声无法滤除;二是电源地平面耦合度差,层间间距过大,分布电容不足;三是电源模块本身纹波大,后端滤波不到位。优化方案:重新布局去耦电容,将小容量高频电容紧贴芯片引脚,补充缺失频段的电容;减小电源地介质厚度,强化平面耦合;在电源模块输出端增加大容量滤波电容和磁珠,隔离电源模块自身噪声。

地弹噪声故障的诊断难度稍高,需要测试芯片接地引脚的电位波动,观察高速信号翻转时的噪声波形。常见诱因是芯片接地引脚过少、接地过孔数量不足、地层碎片化形成孤岛、高速信号回流路径过长。优化方案:在芯片周边增加接地过孔,实现多点接地;修复地层孤岛,保证地层完整性;调整高速信号走线,让回流路径最短,避免绕行;对于多路高速信号,采用分组接地的方式,减少同步翻转的引脚数量,降低瞬态接地电流。

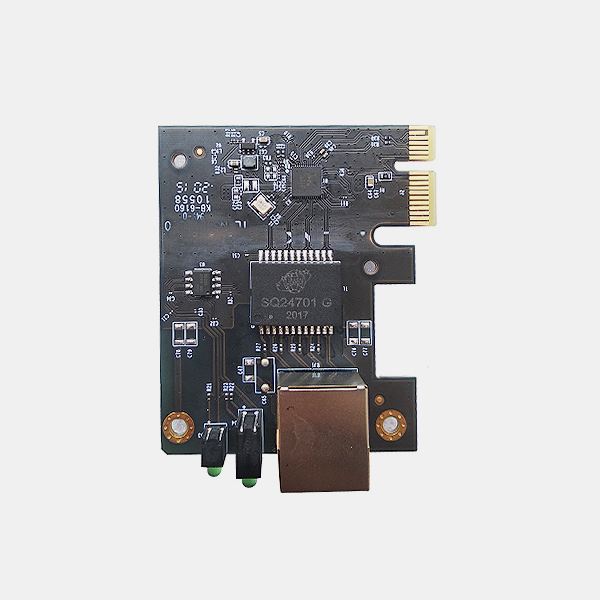

电磁干扰超标引发的电力完整性问题,往往是电源噪声通过辐射向外传播,同时外界干扰也会串入电源回路,形成恶性循环。诊断可通过EMC扫描仪定位干扰源,常见诱因是电源地平面不完整、走线过长形成辐射环路、去耦滤波失效。优化方案:完善电源地平面,封堵平面上的大孔洞和长槽;缩短高频供电走线,减小辐射环路面积;在对外接口处增加滤波电路,比如电容、电感、共模电感,阻断噪声传导路径;全板多余区域铺铜接地,提升屏蔽效果。

除了针对性故障优化,还有三个通用的实操技巧,能快速提升多层PCB电力完整性:一是避免电源走线和高速信号走线平行并行,减少串扰;二是芯片下方尽量不布设信号走线,保证电源地平面完整;三是定期做PDN阻抗仿真测试,尤其是改版设计时,提前预判阻抗问题,避免实物调试返工。

很多工程师觉得电力完整性故障排查很复杂,其实核心逻辑就是“测阻抗、查噪声、找路径”,所有故障都源于PDN阻抗过高、噪声过大、电流路径异常。只要掌握基础的测试方法和优化逻辑,结合PCB设计文件逐一排查,就能快速定位问题根源。而且电力完整性优化是一个循序渐进的过程,先解决压降和基础噪声问题,再优化高频噪声和EMC,逐步提升电路稳定性。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)